Inhaltsverzeichnis

Grund Schaltungen

Flip-Flop

Grobe Unterteilung

- Asynchron (not clocked)

- Synchron (clocked)

- Latch (level triggered)

- Flip-Flop (edge triggered)

FF in slices können auf diverse Arten konfiguriert werden.

Feiner Unterteilung

reset/enable/… synchron/asynchron

D-Latch

process(clk) begin if clk = '1' then q <= d; end if; end process;

D-Flip-Flop

process(clk) begin if clk'event and clk = '1' then q <= d; end if; end process;

D-Flip-Flop + Sync. Enable

process(clk) begin if clk'event and clk = '1' then if enable = '1' then q <= d; end if; end if; end process;

D-Flip-Flop + Sync. Enable + Async. Reset

process(clk, reset) begin if reset = '1' then q <= '0' elseif clk'event and clk = '1' then if enable = '1' then q <= d; end if; end if; end process;

Shift Register

- Haben keinen parallelen Ausgang

- LUT konfigurationen in slice M

- 16-Bit Shift Register

- Distributed RAM

library ieee; use ieee.std_logic_1164.all; entity sr is port( clk: in std_logic; din: in std_logic; dout: out std_logic; ); end sr; architecture behavior of sr is signal tmp: std_logic_vector(7 downto 0); begin process(clk) beginn if clk'event and clk = '1' then for i in 0 to 6 loop tmp(i+1) <= tmp(i); end loop; tmp(0) <= din; end if; end process; dout <= tmp(7); end behavior;

Multiplexer

Gebaut aus LUT gefollt von MUX.

library ieee; use ieee.std_logic_1164.all; entity mux is port( A, B, C, D: in std_logic; S: in std_logic_vector(1 downto 0); O: out std_logic; ); end mux; architectur behavior of mux is begin process(A, B, C, D, S) begin case s is when "00" => O <= A; when "01" => O <= B; when "10" => O <= C; when "11" => O <= D; when others => O <= A; end case; end process; end behavior;

Counter

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity counter is port( clk: in std_logic; reset: in std_logic; Q: out std_logic_vector(3 downto 0); ); end counter; architecture behavior of counter is signal tmp: std_logic_vector(3 downto 0); begin process(clk) begin in clk'event and clk = '1' then if reset = '1' then tmp <= "0000"; else tmp <= std_logic_vector(unsigned(tmp) + 1); end if; end if; end process; Q <= tmp; end behavior;

Additions- und Subtraktionswerk

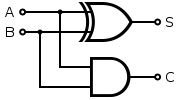

Halbaddierer

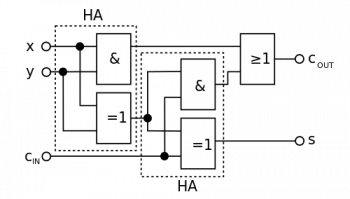

Volladdierer

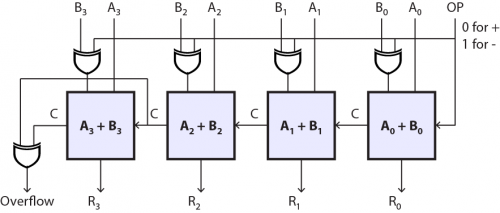

Ripple Carry Adder (RCA)

- Aneinanderreihung von Volladdierern

- Overflow wenn carry in != carry out beim höchstwertigen Bit bei Addition im zweierkompliment

Problem:

- Slow carry propagation

Solution:

- look-ahead carry

- carry-look-ahead

Zweierkompliment

Von links bis ausschließlich der rechtersten 1 negieren.

1 1 1 0 1 1 0 0

0 0 0 1 0 1 0 0

Addition & Subtraktion

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity add_sub is port( asCtl: in std_logic; a: in std_logic_vector(7 downto 0); b: in std_logic_vector(7 downto 0); q: in std_logic_vector(7 downto 0); ); end add_sub; architecture behavior of add_sub is begin process(asCtl, a, b) begin if asCtl = '1' then q <= std_logic_vector(unsigned(a) + unsigned(b)); else q <= std_logic_vector(unsigned(a) - unsigned(b)); end if; end process; end behavior;

Multiplizierer

Verwendete Hardware kann mit Multiplier Style eingestellt werden

- Auto

- Block

- LUT

- Pipe_LUT

Combinatorical path

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity mult is port( clk: in std_logic; a: in std_logic_vector( 7 downto 0); b: in std_logic_vector( 7 downto 0); p: in std_logic_vector(15 downto 0); ); end add_sub; architecture behavior of mult is begin p <= std_logic_vector(unsigned(a) * unsigned(b)); end behavior;

Mit FF

PREG wird gesetzt (Procuct register)

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity mult is port( clk: in std_logic; a: in std_logic_vector( 7 downto 0); b: in std_logic_vector( 7 downto 0); p: in std_logic_vector(15 downto 0); ); end add_sub; architecture behavior of mult is begin process(clk): if rising_edge(clk) then p <= std_logic_vector(unsigned(a) * unsigned(b)); end if; end process; end behavior;

Finite State Machine (FSM)

| Name | Next Stare | Output | Diagramm | |

|---|---|---|---|---|

| Kreis | Transition | |||

| Moore | F(I, S) | F(S) | $\frac{\text{S}}{\text{O}}$ | I |

| Mealy | F(I, S) | F(I, S) | S | I/O |

| Medvedev | F(I, S) | S | $\frac{\text{S}}{\text{O}}$ | I |

asynchrone

Verkettung von:

- transition logic (LUTs o. BRAM)

- state memory (n clocked D-Flip-Flops)

- output logic (optional; LUTs o. BRAM)

⇒ 2^n States möglich

LUT oder BRAM einstellbar im Kontextmenue des Process Window unter Synthesize-XST → Process Properties … → HDL Options → FSM Style

Automatisches Stete encoding (ändern der Nummern der States) unter FSM encoding algorithm (Reduziert anzahl benötigter Komponenten.

Aufbaumöglichkeiten

- Ein Prozess

Alles clock syncron - Zwei Prozesse

- sequenzial process

- state Memory

- combinatorial process

- transition logic

- output logic

- Drei Prozesse

- combinatorial process

- transition logic

- sequenzial process

- state Memory

- combinatorial process

- output logic

Moore

library ieee; use ieee.std_logic_1164.all; entity moore is port( clk: in std_logic; reset: in std_logic; enable: in std_logic; i: in std_logic; o: out std_logic; ); end moore; architecture behavior of moore is signal state: std_logic_vector(1 downto 0); signal nextState: std_logic_vector(1 downto 0); begin -- Combinatorial process (keine clock, Alle Inputs in sensivity list, -- Alle Outputs immer zuweisen (ggf. default Werte)) transitionLogic: process(state, i) begin nextState <= state; case state is when "00" => if i = '1' then nextState <= "01"; else nextState <= "00"; end if; when "01" => if i = '1' then nextState <= "10"; else nextState <= "00"; end if; when "10" => if i = '1' then nextState <= "10"; else nextState <= "00"; end if; when others => nextState <= "00"; end case; end process; -- Sequential process (clock/event gesteuert) stateMemory: process(clk, reset) begin if reset = '1' then state <= "00"; elsif clk'event and clk = '1' then if enable = '1' then state <= nextState; end if; end if; end process; -- Combinatorial process (keine clock, Alle Inputs in sensivity list, -- Alle Outputs immer zuweisen (ggf. default Werte)) outputDecode: process(state) begin if state = "00" then o <= '0'; elsif state = "01" then o <= '0'; elsif state = "10" then o <= '1'; else o <= '0'; end if; end process; end behavior;

Mealy

library ieee; use ieee.std_logic_1164.all; entity mealy is port( clk: in std_logic; reset: in std_logic; enable: in std_logic; i: in std_logic; o: out std_logic; ); end mealy; architecture behavior of mealy is signal state: std_logic; signal nextState: std_logic; begin -- Combinatorial process (keine clock, Alle Inputs in sensivity list, -- Alle Outputs immer zuweisen (ggf. default Werte)) transitionLogic: process(state, i) begin nextState <= state; case state is when '0' => if i = '1' then nextState <= '1'; else nextState <= '0'; end if; when '1' => if i = '1' then nextState <= '1'; else nextState <= '0'; end if; when others => nextState <= '0'; end case; end process; -- Sequential process (clock/event gesteuert) stateMemory: process(clk, reset) begin if reset = '1' then state <= '0'; elsif clk'event and clk = '1' then if enable = '1' then state <= nextState; end if; end if; end process; -- Combinatorial process (keine clock, Alle Inputs in sensivity list, -- Alle Outputs immer zuweisen (ggf. default Werte)) outputLogic: process(state, i) begin if state = '1' and i = '1' then o <= '1'; else o <= '0'; end if; end prcess; end behavior;

Medvedev

BRAM

Erstellen per Edit → Language Templates.

Verwendtet shared variable

Optionen

- RAM Extraction

- On

- Off

- RAM style

- Auto

- Distributed

- Block

Numbers

Typen

| Name | In | Bereich |

|---|---|---|

integer | Sprache | - bis + |

natural | Sprache | 0 bis + |

signed | ieee.numeric_std | - bis + |

unsigned | ieee.numeric_std | 0 bis + |

std_logic_vector | ieee.std_logic_1164 | – |

Operationen

Berechnungen

Funktionen:

+ | - | * | / | rem | mod | < | <= | > | >= | = | /= |

Argumente:

unsigned/natural | unsigned/natural |

signed/integer | signed/integer |

Rotationen

Funktionen:

sll | srl | rol | ror |

Argumente:

signed | integer |

unsigned | integer |

Logik

Funktionen:

not | and | or | nand | nor | xor | xnor |

Argumente:

signed | signed |

unsigned | unsigned |

Typumwandlungen

| von | mit | nach |

|---|---|---|

signed unsigned | y <= to_integer(x) | integer |

integer | y <= to_signed(x, y'length) | signed |

integer | y <= to_unsigned(x, y'length) | unsigned |

std_logic_vector unsigned | y <= signed(x) | signed |

std_logic_vector signed | y <= unsigned(x) | unsigned |